바이너리 디코더 설명: 유형, 기능 및 애플리케이션

2026-04-23

176

카탈로그

바이너리 디코더의 기본

에이 바이너리 디코더 는 조합 논리 회로 이는 변형되거나 n비트 바이너리 입력 이름까지 2개의 고유한 출력 라인.각 출력은 특정 입력 조합에 해당합니다.

간단히 말해서 디코더는 이진 데이터를 가능한 많은 출력 중 하나로 변환합니다.일반적으로 인코더와 반대되는 것으로 간주됩니다.

대부분의 디코더에는 회로가 작동하는지 여부를 확인하는 활성 입력이 포함되어 있습니다.비활성화되면 모든 출력이 비활성화된 상태로 유지됩니다.

바이너리 디코더의 작동 방식

디코더를 활성화합니다 한 줄 결과 입력의 조합을 기반으로 합니다. 입력 신호는 다음을 사용하여 생성됩니다. 문이 아니다 변신하고 그리고 문 통합을 통해 적절한 생산 주기를 허용합니다.어떤 결과라도 단일 입력 조합, 활성 입력이 디코더인지 아닌지를 결정할 때 활성.

일반적인 유형의 바이너리 디코더

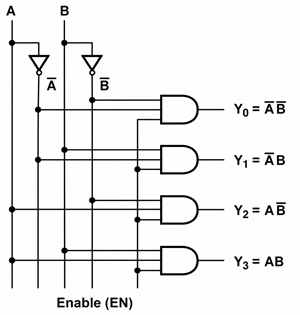

2-4 디코더

2-4 디코더에는 2개의 입력 라인과 4개의 출력 라인이 있습니다.단순한 설계와 쉬운 구현으로 인해 기본적인 디지털 회로에 자주 사용됩니다.

사실 자료:

|

에이 |

비 |

출구 |

|

0 |

0 |

Y0 |

|

0 |

1 |

Y1 |

|

1 |

0 |

Y2 |

|

1 |

1 |

Y3 |

3-8 디코더

3-8 디코더에는 3개의 입력 라인과 8개의 출력 라인이 있습니다.이는 일반적으로 메모리 주소 지정 및 제어 시스템에 사용되며 이진-8진 디코더라고도 합니다.

사실 자료:

|

에이 |

비 |

C |

활성

출구 |

|

0 |

0 |

0 |

Y0 |

|

0 |

0 |

1 |

Y1 |

|

0 |

1 |

0 |

Y2 |

|

0 |

1 |

1 |

Y3 |

|

1 |

0 |

0 |

Y4 |

|

1 |

0 |

1 |

Y5 |

|

1 |

1 |

0 |

Y6 |

|

1 |

1 |

1 |

Y7 |

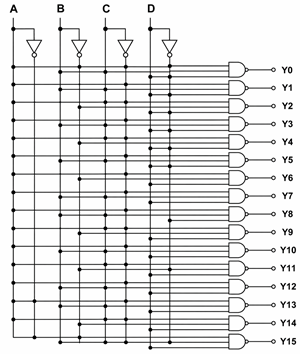

4-16 디코더

4-16 디코더에는 4개의 입력 라인과 16개의 출력 라인이 있습니다.이는 복잡한 디지털 시스템에 사용되며 더 많은 출력 옵션이 필요한 대규모 설계에 적합합니다.

사실 자료:

|

에이 |

비 |

C |

디 |

활성

출구 |

|

0 |

0 |

0 |

0 |

Y0 |

|

0 |

0 |

0 |

1 |

Y1 |

|

0 |

0 |

1 |

0 |

Y2 |

|

0 |

0 |

1 |

1 |

Y3 |

|

0 |

1 |

0 |

0 |

Y4 |

|

0 |

1 |

0 |

1 |

Y5 |

|

0 |

1 |

1 |

0 |

Y6 |

|

0 |

1 |

1 |

1 |

Y7 |

|

1 |

0 |

0 |

0 |

Y8 |

|

1 |

0 |

0 |

1 |

Y9 |

|

1 |

0 |

1 |

0 |

Y10 |

|

1 |

0 |

1 |

1 |

Y11 |

|

1 |

1 |

0 |

0 |

Y12 |

|

1 |

1 |

0 |

1 |

Y13 |

|

1 |

1 |

1 |

0 |

Y14 |

|

1 |

1 |

1 |

1 |

Y15 |

입력 개수가 증가하면 출력 개수도 기하급수적으로 늘어납니다.

바이너리 디코더의 설계

1단계: 입력과 출력 정의

입력: A, B

출력: Y0, Y1, Y2, Y3

2단계: 사실 시트

|

입력

(AB) |

출구 |

|

00 |

Y0 |

|

01 |

Y1 |

|

10 |

Y2 |

|

11 |

Y3 |

3단계: 부울 표현식

• Y0 = A'B'

• Y1 = A'B

• Y2 = AB'

• Y3 = AB

4단계: 구현

• A'와 B'를 생성하려면 NOT 게이트를 사용하세요.

• AND 게이트를 사용하여 결과 생성

바이너리 디코더를 사용한 논리 함수

구현을 위해 바이너리 디코더를 사용할 수 있습니다. 부울 함수 왜냐하면 모든 출구가 최소학기 특정 출력을 선택하고 조합하여 복잡한 논리 기능을 구현할 수 있습니다.

예:

F(A, B, C) = Σ(1, 3, 5, 7)

이진 디코더를 사용하여 이 기능을 구현하려면 입력 변수가 3개이므로 3-to-8 이진 디코더를 사용합니다.입력을 연결하세요 에이, 비, 그리고 C 디코더 입력에서 민터맨과 일치하는 출력을 선택하십시오. 1, 3, 5, 그리고 7(Y1, Y3, Y5 및 Y7).마지막으로, 이 제품은 또는 OR 게이트 원하는 출력을 생성합니다.

OR 게이트의 출력은 필요한 부울 함수를 제공합니다.

바이너리 디코더 IC(74LS137)

그림 6. 74LS137 3-to-8 디코더 IC 핀 다이어그램

는 74LS137 비트 용량을 갖춘 3x8 디코더입니다.세 개의 입력 라인이 있습니다 (A, B, C) 8개의 출력 라인 (Y0~Y7), 제어를 위한 활성화 버튼이 있습니다.또한 입력 값을 저장하는 내장 루프도 포함되어 있습니다.

이 디코더에서는 출력이 활성화됩니다. 낮음, 즉, 제품을 선택하면 다음과 같이 됩니다. 0 (낮음) 대신 1, 다른 모든 제품은 그대로 유지됩니다. 높음.

메모리 시스템에서는 디코더를 사용하여 여러 개의 메모리 칩 중에서 하나의 메모리 칩을 선택할 수 있습니다.선택한 라인만 LOW가 되어 특정 칩을 활성화합니다.

|

핀

아니요. |

핀

편지 |

유형 |

설명 |

|

1 |

에이 |

입력 |

입력 선택(LSB) |

|

2 |

비 |

입력 |

입력 선택 |

|

3 |

C |

입력 |

입력 선택(MSB) |

|

4 |

GL̅ |

활성화/비활성화 |

활성 LOW 감소 활성화 |

|

5 |

G2̅ |

활성화 |

활성 LOW 활성화 |

|

6 |

G1 |

활성화 |

액티브 HIGH 활성화 |

|

7 |

Y7 |

출구 |

출력 라인 7(액티브 LOW) |

|

8 |

접지 |

힘 |

지구 |

|

9 |

Y6 |

출구 |

출력 라인 6(액티브 LOW) |

|

10 |

Y5 |

출구 |

출력 라인 5(액티브 LOW) |

|

11 |

Y4 |

출구 |

출력 라인 4(액티브 LOW) |

|

12 |

Y3 |

출구 |

출력 라인 3(액티브 LOW) |

|

13 |

Y2 |

출구 |

출력 라인 2(액티브 LOW) |

|

14 |

Y1 |

출구 |

출력 라인 1(액티브 LOW) |

|

15 |

Y0 |

출구 |

출력 라인 0(활성 LOW) |

|

16 |

Vcc |

힘 |

+ 5V 공급 |

바이너리 디코더 사용

• 메모리 주소 디코딩

• 프로세서의 명령어 디코딩

• 기기 선택

• 7부작 일러스트레이션

• 데이터 관리 시스템

바이너리 디코더와 디멀티플렉서

|

특징 |

바이너리

디코더 |

디멀티플렉서 |

|

기능 |

하나의 출력 라인을 선택합니다. |

데이터를 하나의 출력으로 보냅니다. |

|

입력 |

바이너리 입력 코드 |

데이터 입력 + 선택한 라인 |

|

작업 |

하나의 결과를 활성화합니다. |

데이터 흐름을 간소화합니다. |

|

사용하다 |

선택/제어 |

데이터 배포 |

결과

바이너리 디코더는 여러 옵션에서 올바른 출력을 선택하여 디지털 회로를 단순화하는 데 도움이 됩니다.이는 메모리 시스템, 프로세서 및 제어 애플리케이션에 널리 사용됩니다.이를 이해하면 디지털 전자 개념을 더 쉽게 배우고 적용할 수 있습니다.

뜨거운 기사

- LM358 듀얼 작동 증폭기 포괄적 인 가이드 : 핀아웃, 회로도, 등가, 유용한 예제

- CR2032 및 CR2016 상호 교환 가능합니까?

- 차이 이해 ESP32 및 ESP32-S3 기술 및 성능 분석

- 올바른 배터리 선택 : AG4, LR626, LR66, 177/376/377, SR626 및 SR626SW에 대한 가이드

- NPN vs. PNP : 차이점은 무엇입니까?

- BC547 트랜지스터 기본: 핀 배치, 응용 회로, 대체/보완 모델

- ESP32 vs STM32 : 어떤 마이크로 컨트롤러가 더 낫습니까?

- MOSFET이란 무엇이며 작동 방식은 무엇입니까?

- 전기 릴레이 기본 : 작업 작동, 유형 및 사용

- PNP 트랜지스터 : 구조, 작업 원리 및 응용 프로그램

ASIC과 FPGA: 어느 것을 선택해야 할까요?

ASIC과 FPGA: 어느 것을 선택해야 할까요?

2026-04-24

공동 패키지 광학(CPO)이란 무엇입니까?개요, 이점 및 응용

공동 패키지 광학(CPO)이란 무엇입니까?개요, 이점 및 응용

2026-04-23

자주 묻는 질문 [FAQ]

1. 회로에 적합한 디코더를 선택하는 방법은 무엇입니까?

입력 변수의 수, 필요한 출력, 작동이나 래칭과 같은 기능이 필요한지 여부를 기준으로 디코더를 선택하십시오.

2. 마이크로컨트롤러에 바이너리 디코더를 사용할 수 있나요?

예, 디코더는 마이크로 컨트롤러에서 주소를 디코딩하고 메모리 또는 주변 장치를 선택하는 데 사용됩니다.

3. 전파 지연은 디코더 회로에 어떤 영향을 줍니까?

전파 지연으로 인해 입력 변경과 변경 사이에 약간의 지연이 발생합니다. 결과적인 응답은 고속 디지털 시스템에 영향을 미칠 수 있습니다.

5. 바이너리 디코더를 계단식으로 연결할 수 있나요?

예, 디코더를 캐스케이드 연결하여 더 큰 디코더를 생성할 수 있습니다. 더 작은 디코더를 사용하여 4-16 디코더를 구축하는 것과 같은 디코더.

6. 메모리 시스템에서 디코더의 역할은 무엇입니까?

디코더는 한 번에 하나의 주소 라인을 활성화하여 특정 메모리 위치를 선택하고 올바른 데이터 액세스를 보장합니다.

핫 부품 번호

GRT32DR61A226ME01L

GRT32DR61A226ME01L GRT32ER60J107ME13L

GRT32ER60J107ME13L CC0402CRNPO9BNR68

CC0402CRNPO9BNR68 GRM21BC81E106ME11K

GRM21BC81E106ME11K C2012X8R2A683K125AE

C2012X8R2A683K125AE 06031A330JAJ2A

06031A330JAJ2A TAP226K020CCS

TAP226K020CCS JANTX2N2907A

JANTX2N2907A IXGN100N160A

IXGN100N160A Z84C3008PEG

Z84C3008PEG

- MB9BF106NPMC-G-JNE1

- STM32F051K8U6TR

- PIC16F636-I/P

- EDW4032CABG-50-N-F-D

- V375B28T300BL

- RT0603DRD07920RL

- EPM3128ATI144-10N

- MC68HC705C9ACP

- AT89S8253-24PI

- MC33780EG

- XZFABBA10A

- CB1AH-12V

- LQW18ANR39G8ZD

- 2MBI100S-120

- 7MBR15UA120-50

- LTC6433AIUF-15#PBF

- XC3S1000-4FTG256C

- LTC6253IDC#TRMPBF

- TS5A12301EYFPR

- THS4032CDGNRG4

- 215LKAAKA11FG

- FM1182P-GE

- LC75834W

- LT1641CS8#TR

- NAND02GW3B2DNB

- TC4069UBP

- VNQ6004AS

- 39WF800B-70-4I-B3KE

- ACFM-2113-TR1

- INL868GN

- K4N56163QG-ZC2A

- MB95F564KPF-G-UNE2

- TC90455XBG

- XC9801B333KR

- IT8585E-FXA

- BP5158H

- ICM-42605

- 586-1106-101F

- RN1406LF