FPGA를위한 키드 단일 펄스 생성기 설계 : 펄스 폭 및 위상 동기화

2024-12-17

5110

목록

소개

FPGA 개발 영역에서 정확한 단일 펄스를 제작하면 다양한 응용 프로그램이 있습니다.이 펄스는 때때로 클록 사이클과 동기화없이 작동하며, 최대한 정밀도가 간과 될 때만 허용됩니다.그러나 일부 애플리케이션은 클록 사이클에 따라 폭과 위상에서 완벽하게 정렬되므로 키가 깔린 단일 펄스 생성기를 사용해야합니다.키 프레스에 의해 활성화 된이 발전기는 일관된 펄스를 생성하여 독특한 과제, 특히 FPGA 보드에 대한 시계 유발 지터의 영향을 제시하는 것을 목표로합니다.

동기화의 도전

주요 프레스 타이밍의 예측할 수없는 특성으로 인해 지터와 같은 변수의 영향을받는 수동 트리거 펄스는 종종 기술적 문제에 직면합니다.실용적인 솔루션은 혼란스러운 키 입력을 길들이도록 복잡하게 설계된 분동 회로를 배치하는 것입니다.이 회로는 노이즈를 효율적으로 필터링하고 입력 신호를 안정화시켜 안정적인 단일 펄스 생성을 촉진합니다.실제 응용 분야에서 엔지니어는 과거의 경험에서 지혜를 끌어내어 이러한 회로를 통합하면 시스템 신뢰성이 크게 향상된다는 것을 보여줍니다.

시계 유발 지터에 대처합니다

시계로 인한 지터는 지속적으로 도전을 제기하여 펄스 타이밍을 잠재적으로 방해합니다.이 문제는 시계 기간의 V ariat 이온에서 나오는 특정 작업에 필수적인 타이밍을 변경할 수 있습니다.지터 관리는 사려 깊은 회로 설계 및 효과적인 FPGA 리소스 활용에 의한 결과입니다.지터를 최소화하는 데있어 펄스 생성기는 예상 정밀도를 유지하도록합니다.철저한 테스트와 정확한 교정을 통해 전문가들은 시스템을 미세 조정하여 성능 표준을 능가합니다.

고급 펄스 생성 기술을 수용합니다

완벽한 펄스 생성을 추구하려면 정교한 방법론을 채택해야합니다.에지 감지 및 신호 조절과 같은 기술은 펄스 충실도를 증폭시키는 데 사용됩니다.인지 적 접근법으로부터 추가로 차입하면 적응 형 알고리즘은 미묘하게 입력을 안정화시킬 수 있습니다.고급 전략의 신중한 구현은 불필요한 스포트라이트를 피하면서 시스템 성능을 조용히 최적화합니다.

FPGA 개발의 주요 분해 및 단일 펄스 생성기

분해 회로 제작

효과적인 키 분해 회로를 설계하면 카운터의 영리한 통합이 필요합니다.이 카운터는 산만 한 노이즈를 필터링하고 입력 신호의 안정성을 고정시키는 데 필수적입니다.카운터의 크기는 예상 지터의 펄스 지속 시간과 클록의 샘플링 주파수 사이의 상호 작용에 달려 있습니다.5 ~ 10 밀리 초의 범위로 식별 된 일반적인 지터 기간을 수용하기 위해 24MHz 시스템 시계에 효과적인 20 비트 카운터 모듈러스를 고려할 수 있습니다.목표는 22 밀리 초 근처에 지연을 심어 일관성의 신호 만 이동하여 키 스트로크를 정확하게 등록하는 것입니다.운영 중에 키 프레스를 감지하면 카운터는 시합을 시작하고 수를 충족시킬 때 안정적인 신호를 인식하여 안전한 펄스 생성을 용이하게합니다.

키 제어 단일 펄스 발전기 회로의 원리

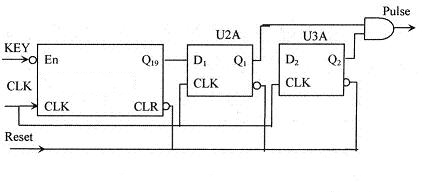

키 제어 단일 펄스 생성기는 위에서 언급 한 회로를 사용하여 주요 분동 문제를 해결하고 안정적인 신호를 얻습니다.그림 1과 같이 두 개의 D 플립 플롭과 AN 및 게이트를 사용하여 단일 펄스를 생성합니다.

D 플립 플롭 U2A는 안정적인 신호 D1 = 1을 수신 한 후 트리거됩니다.플립 플롭 U2A의 Q1 터미널은 CLK와 동기화 된 양의 펄스를 얻습니다.출력 Q1 ~ D Flip-Flop U3A, Q1보다 한 클록 사이클에 의해 양의 펄스가 지연되고 Q2의 출력을 반전하여 음의 펄스를 얻습니다.AN 및 GATE의 입력으로 Q1 및 QN2의 출력은 원래 클록 사이클의 두 배로 펄스 폭으로 단일 펄스를 출력합니다.

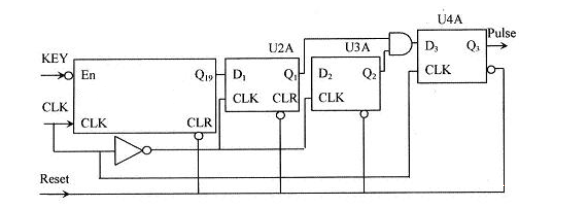

단일 펄스의 펄스 폭을 클럭주기와 동일하게 및 클럭주기와 동일한 단계로 만들기 위해도 1의 회로 설계가 개선된다.

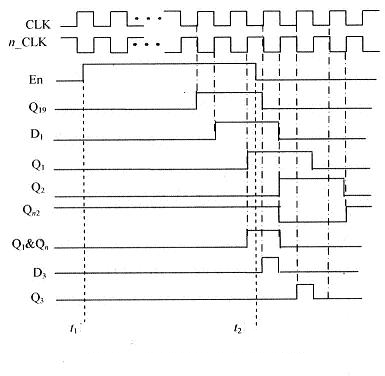

그림 2에서는 시계가 D 플립 플롭으로 전송되기 전에 게이트가 추가되어 Q1 터미널이 NCLK (CLK의 리버스 펄스 신호)와 동기화 된 양의 펄스를 생성 할 수 있도록, 및 게이트는 단일 펄스 및 CLK가 출력합니다.플립 플롭 U4A의 입력 D4가 Clk U4a의 상승 가장자리에서 트리거되어 단일 펄스의 펄스 폭이 클록 사이클과 동일하고 동일한 펄스 폭은 동일 한 펄스 폭이 있습니다.실현되었습니다.출력 펄스가 클록 사이클에 해당하여 위상 조정을 달성하기 위해 절반 클록 사이클에 의해 지연됩니다.전체 단일 펄스 생성기의 타이밍 다이어그램은 그림 3에 나와 있습니다 (그림 3의 T1 및 T2는 키가 눌리고 키가 올라가는 모멘트입니다).

FPGA의 주요 분동 카운터 및 단일 펄스 생성기를 기반으로 한 Verilog HDL 언어 설명

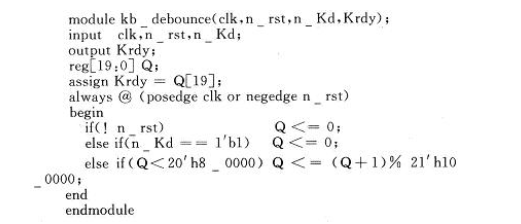

그림 1의 주요 분동 카운터 회로에서 설명 할 Verilog HDL 언어 코드는 다음과 같습니다.

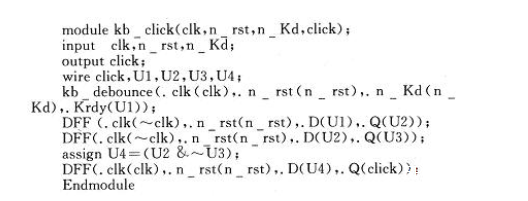

코드의 N_RST 및 KEY N_KD의 재설정은 모두 활성입니다.키드 단일 펄스 생성기의 Verilog HDL 언어 코드는 다음과 같습니다.

D Flip-Flop DFF는 코드에도 사용 되며이 모듈을 구현하려는 코드는 비교적 간단합니다.

결론

이 디자인은 클록 사이클과 동기화 된 키로 된 단일 펄스 생성기를 성공적으로 소개하며, 펄스 폭과 위상 모두에서 쇠퇴 도전에 대처합니다.적용 가능성은 정확한 단일 펄스 출력이 수요가있는 광범위한 FPGA 응용 프로그램에 걸쳐 확장됩니다.Debounce Circuit은 다양한 FPGA 구성에 맞는 인상적인 적응성을 보여줍니다.특정 프로젝트 요구를 위해 제작 된 카운터는 계수 조정을 통합하여 다양한 지터 조건을 적절하게 처리하여 응용 프로그램의 다양성을 향상시킵니다.

뜨거운 기사

- LM358 듀얼 작동 증폭기 포괄적 인 가이드 : 핀아웃, 회로도, 등가, 유용한 예제

- CR2032 및 CR2016 상호 교환 가능합니까?

- 차이 이해 ESP32 및 ESP32-S3 기술 및 성능 분석

- 올바른 배터리 선택 : AG4, LR626, LR66, 177/376/377, SR626 및 SR626SW에 대한 가이드

- BC547 트랜지스터 기본: 핀 배치, 응용 회로, 대체/보완 모델

- NPN vs. PNP : 차이점은 무엇입니까?

- ESP32 vs STM32 : 어떤 마이크로 컨트롤러가 더 낫습니까?

- MOSFET이란 무엇이며 작동 방식은 무엇입니까?

- 전기 릴레이 기본 : 작업 작동, 유형 및 사용

- PNP 트랜지스터 : 구조, 작업 원리 및 응용 프로그램

프로그래밍 가능한 장치의 진화 이해 : PAL에서 FPGA까지

프로그래밍 가능한 장치의 진화 이해 : PAL에서 FPGA까지

2024-12-17

SKM800GA176D Semikron PDF 데이터 시트, 기호, 포장

SKM800GA176D Semikron PDF 데이터 시트, 기호, 포장

2024-12-17

핫 부품 번호

C1005X5R1V334M050BC

C1005X5R1V334M050BC C1005NP01H271J050BA

C1005NP01H271J050BA CGA9N3X7R2E474M230KA

CGA9N3X7R2E474M230KA 12063C474KAZ2A

12063C474KAZ2A 12065C103MAT4A

12065C103MAT4A 06035C563JAT2A

06035C563JAT2A 06035A470JAJ2A

06035A470JAJ2A GRM1556R1H7R8CZ01D

GRM1556R1H7R8CZ01D TAJB106K020K

TAJB106K020K 1-1469491-2

1-1469491-2

- TAJC475K050RNJ

- MAX5541ESA+T

- LCMXO640C-3F256C

- PIC18LF13K22-I/SO

- XR16V654IV80-F

- ACPL-332J-500E

- EPM3064ATI44-10N

- RT0805BRD07102RL

- PE43503MLI

- CM50DU-12H

- MCC56-06i08

- LTC3114EDHC-1#PBF

- T491D476K016AGZB06

- TPS73HD301PWP

- ADUM2400CRIZ

- AD623BRZ

- L9177ATR

- LMV934Q1MTX/NOPB

- NC7SZ32M5X

- BTS711L1XUMA1

- BCM53115UKFBG

- CMSH1-60MTR13

- FDC37C935QF

- HMC251MS8E

- K7R320884M-FC25

- MT90820AP

- PALC22V10B-15JI

- R5F2132DNSP#UO

- R5F21336ANFP#V2

- SC1159SW.TR

- UPD780308GC-A01-8EU

- MSP4458G

- PESD5V0F1BLD

- TLSR8516EP16

- KLU1S516E1LF

- L8560AAU

- AD2S1210WBSTZ

- CY7B994V-2AI

- UCC21750DW