래치 및 에지 트리거 플립플롭 이해

2026-04-21

160

카탈로그

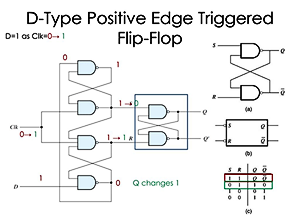

그림 1. 포지티브 에지 트리거 D 플립플롭

에지 트리거 래치 및 플립플롭 개요

디지털 전자제품에서는 래치 및 플립플롭 데이터를 저장하는 데 사용되는 간단한 부품입니다. 0 또는 1.카운터, 레지스터, 프로세서 등 정보를 기억해야 하는 회로에 필요합니다.

래치는 간단한 방식으로 작동합니다.켜져(활성화)되어 있는 한 입력이 변경될 때마다 출력이 변경됩니다.그 결과 빠르게 반응하지만, 입력이 안정적이지 않으면 잘못된 시점에 변할 수도 있습니다.

플립플롭은 다르게 작동합니다.이는 특정 순간에만 출력을 변경합니다. 클록 신호의 에지.이는 다음과 같습니다.

• A 상승 에지 (신호가 로우에서 하이로 바뀔 때)

• A 떨어지는 가장자리 (신호가 높음에서 낮음으로 바뀔 때)

이 동작을 에지 트리거링.에지 트리거링은 데이터 저장 시기를 제어하는 데 도움이 됩니다.항상 변경하는 대신 플립플롭은 클록 신호의 정확한 순간에만 업데이트됩니다.이는 회로를 더욱 안정적이고 신뢰할 수 있게 만듭니다.

래치란 무엇입니까?

래치는 1비트의 데이터(0 또는 1)를 저장하고 변경이 허용될 때까지 해당 값을 유지하는 간단한 전자 부품입니다.래치는 활성화 신호를 사용하여 작동을 제어합니다.활성화되면 래치가 입력을 출력으로 직접 전달합니다.비활성화되면 입력이 변경되더라도 마지막으로 저장된 값을 유지합니다.활성화된 동안 언제든지 업데이트할 수 있으므로 빠르게 반응하지만 올바른 작동을 위해서는 안정적인 입력 신호가 필요합니다.

플립플롭이란 무엇입니까?

플립플롭은 1비트의 데이터(0 또는 1)를 저장하고 클록 신호에 의해 제어되는 특정 순간에만 출력을 업데이트하는 디지털 메모리 장치입니다.플립플롭은 시계의 변화에 반응하여 정확한 시간에 입력 데이터를 캡처할 수 있습니다.이로 인해 작동이 더욱 제어되고 예측 가능해지기 때문에 정확한 타이밍이 필요한 시스템에 플립플롭이 사용됩니다.

래치와 플립플롭: 주요 차이점

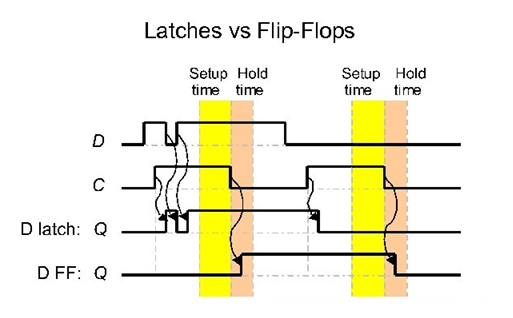

그림 2. 래치 대 플립플롭 타이밍 다이어그램

래치와 플립플롭은 모두 1비트의 데이터를 저장하는 데 사용되지만 작동 방식은 다릅니다.래치와 플립플롭의 간단한 비교는 다음과 같습니다.

|

특징 |

래치 |

플립플롭 |

|

제어 신호 |

신호 활성화 |

시계 신호 |

|

트리거 유형 |

레벨 트리거 |

에지 트리거 |

|

출력변화 |

언제라도 변한다

활성화됨 |

시계에서만 변경됩니다.

전환 |

|

타이밍 제어 |

덜 정확함 |

더욱 정확하고

통제된 |

|

안정성 |

더 낮음(에 따라 다름)

입력 안정성) |

더 높음(업데이트 시간:

정확한 순간) |

|

복잡성 |

심플한 디자인 |

더욱 복잡한 디자인 |

|

속도 |

더 빠른 응답 |

약간 느림(

시계) |

|

일반적인 사용 |

간단하거나 저렴한 비용

회로 |

동기식 디지털

시스템 |

에지 트리거링이란 무엇입니까?

에지 트리거링 입력 변화에 지속적으로 반응하지 않고 신호 상태가 변경되는 정확한 순간에만 장치가 출력을 업데이트하는 디지털 회로에 사용되는 방법입니다.이러한 신호의 변화를 신호라고 합니다. 가장자리, 신호가 다음에서 전환될 때 발생합니다. 낮은 것에서 높은 것 (로 알려짐 상승 에지) 또는 높은 것에서 낮은 것(으로 알려짐) 떨어지는 가장자리).이러한 특정 전환 지점에서만 반응함으로써 에지 트리거 장치는 정확한 순간에 데이터를 캡처하고 저장할 수 있습니다.입력이 자주 변경되거나 불안정할 경우 발생할 수 있는 무작위 또는 원치 않는 업데이트를 방지하기 때문에 이러한 제어된 동작이 필요합니다.결과적으로 에지 트리거링을 사용하면 디지털 시스템이 보다 체계적이고 예측 가능한 방식으로 작동하여 의도한 경우에만 데이터가 처리되고 저장되도록 할 수 있습니다.

에지 트리거링 작동 방식

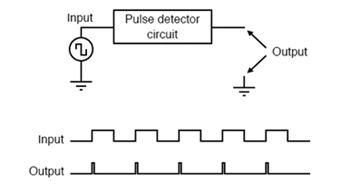

그림 3. 엣지 감지 회로

에지 트리거링은 클록 신호 상태가 변경되는 정확한 순간에만 디지털 회로가 출력을 업데이트하도록 허용함으로써 작동합니다.입력 신호에 지속적으로 응답하는 대신 회로는 입력 값을 캡처하기 전에 낮은 수준에서 높은 수준(상승 에지) 또는 높은 수준에서 낮은 수준(하강 에지)으로의 클록 전환을 기다립니다.

회로 내부에서 이 동작은 클록 신호의 변화를 감지하는 논리 게이트 또는 내부 단계의 조합을 사용하여 달성됩니다.에지가 발생하는 순간 입력 데이터는 잠시 통과된 후 출력으로 저장됩니다.이 순간 이후 회로는 다음 클록 전환까지 추가 입력 변경을 무시합니다.

이 방법을 사용하면 정확하고 통제된 시간에 데이터를 캡처할 수 있습니다.클럭 에지 사이에 입력이 여러 번 변경되더라도 정확한 전환에 존재하는 값만 저장됩니다.이렇게 하면 원치 않는 업데이트를 방지하고 시스템을 안정적으로 유지하는 데 도움이 됩니다.

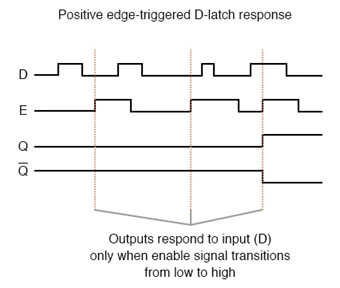

포지티브 에지 트리거링(상승 에지)

그림 4. 포지티브 에지 트리거 타이밍 다이어그램

상승 에지 트리거링이라고도 하는 포지티브 에지 트리거링은 클록 신호가 로우(0)에서 하이(1)로 변경될 때만 회로의 출력을 업데이트하는 방법입니다.이 순간을 상승 에지라고 합니다.

이러한 유형의 작동에서 회로는 대부분의 경우 입력 변경을 무시합니다.상승 에지가 발생하는 순간에만 입력값을 확인하고 저장합니다.데이터가 캡처되면 입력이 중간에 변경되더라도 다음 상승 에지까지 출력이 동일하게 유지됩니다.

이 접근 방식은 예측 가능한 특정 순간에만 데이터가 업데이트되도록 보장하므로 타이밍을 더 효과적으로 제어할 수 있습니다.또한 불안정하거나 잡음이 많은 입력 신호로 인해 발생하는 원치 않는 변경을 줄이는 데도 도움이 됩니다.

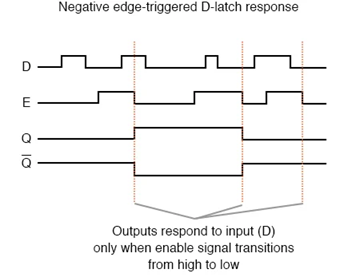

네거티브 에지 트리거링(하강 에지)

그림 5. 네거티브 에지 트리거 타이밍 다이어그램

하강 에지 트리거링이라고도 하는 네거티브 에지 트리거링은 클록 신호가 하이(1)에서 로우(0)로 변경될 때만 회로의 출력을 업데이트하는 방법입니다.이 순간을 하강 에지(falling edge)라고 합니다.

이러한 유형의 작동에서는 회로가 입력 변화에 지속적으로 응답하지 않습니다.Falling Edge가 발생하는 순간에만 입력값을 확인하여 저장합니다.그 이후에는 입력이 중간에 변경되더라도 다음 하강 에지까지 출력이 변경되지 않은 상태로 유지됩니다.

이러한 제어된 동작은 데이터가 정확한 시간에 업데이트되도록 보장하여 불안정한 신호로 인해 발생하는 원치 않는 변경 가능성을 줄여줍니다.타이밍을 주의 깊게 관리해야 하거나 클록의 하강 에지에서 작동이 발생하도록 설계된 시스템에는 네거티브 에지 트리거 회로가 필요합니다.

플립플롭의 클록 신호

클록 신호는 플립플롭이 출력을 업데이트할 수 있는 시기를 제어하는 반복되는 디지털 신호입니다.이는 타이밍 가이드 역할을 하여 데이터가 올바른 순간에 저장되도록 합니다.클록 신호는 낮은(0)과 높은(1) 사이를 지속적으로 전환하여 플립플롭이 따르는 규칙적인 패턴을 만듭니다.

플립플롭에서는 클럭 신호가 입력 데이터를 읽고 저장할 시기를 결정합니다.입력이 변경될 때마다 출력을 변경하는 대신 플립플롭은 상승 에지 또는 하강 에지와 같은 클록 신호의 특정 지점을 기다립니다.정확한 순간에 입력 값이 캡처되어 출력으로 저장됩니다.

이러한 타이밍 제어는 디지털 시스템의 모든 부분이 동기화된 방식으로 함께 작동하도록 유지하기 때문에 필요합니다.입력이 서로 다른 시간에 변경되더라도 플립플롭은 클록 신호에서만 업데이트되므로 오류와 원치 않는 변경이 방지됩니다.

플립플롭의 동기 입력

플립플롭의 동기 입력은 클록 신호에 의해 제어되는 입력입니다.이는 플립플롭이 클록의 상승 또는 하강 에지와 같은 특정 순간에만 이러한 입력을 읽고 응답한다는 것을 의미합니다.

플립플롭에서 D(데이터), S(설정) 또는 R(리셋)과 같은 입력은 적용 시 출력을 즉시 변경하지 않습니다.대신 플립플롭은 클록 신호가 올바른 전환에 도달할 때까지 기다립니다.정확한 순간에 입력 값을 캡처하고 출력을 업데이트합니다.

이 동작을 통해 회로의 모든 변경 사항은 시기적절하고 체계적인 방식으로 발생합니다.입력 신호가 여러 번 변경되더라도 클럭 에지에 있는 값만 사용됩니다.이는 오류를 방지하고 시스템을 안정적으로 유지하는 데 도움이 됩니다.

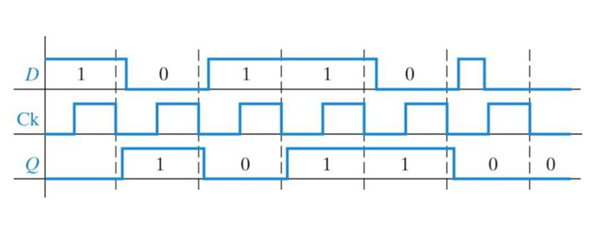

에지 트리거 플립플롭의 타이밍 다이어그램

그림 6. D 플립플롭 타이밍 다이어그램

타이밍 다이어그램은 디지털 회로에서 시간이 지남에 따라 신호가 어떻게 변하는지를 시각적으로 보여주는 방법입니다.에지 트리거 플립플롭의 경우 클록 신호 및 입력 데이터와 관련하여 출력이 변경되는 시기를 설명하는 데 도움이 됩니다.

일반적인 타이밍 다이어그램에는 세 가지 주요 신호가 표시됩니다.

• 시계(CLK) – 타이밍을 제어하는 반복 신호

• 입력(D, S 또는 R) – 플립플롭에 적용되는 데이터

• 출력(Q) – 저장된 값

에지 트리거 플립플롭의 주요 아이디어는 출력이 클록 에지에서만 변경된다는 것입니다.상승 에지 플립플롭인 경우 클럭이 로우에서 하이로 바뀔 때만 출력이 업데이트됩니다.하강 에지 플립플롭인 경우 클록이 하이에서 로우로 바뀔 때 업데이트가 발생합니다.

이러한 가장자리 사이에서는 입력이 변경되더라도 출력은 동일하게 유지됩니다.클럭 에지의 정확한 순간에 입력된 값만 캡처되어 저장됩니다.

타이밍 다이어그램은 클록 전환이 발생하는 지점과 출력이 이러한 전환을 따르는 방식을 표시하여 이러한 동작을 명확하게 보여줍니다.이를 통해 플립플롭이 제어되고 예측 가능한 방식으로 데이터를 저장하는 방법을 더 쉽게 이해할 수 있습니다.

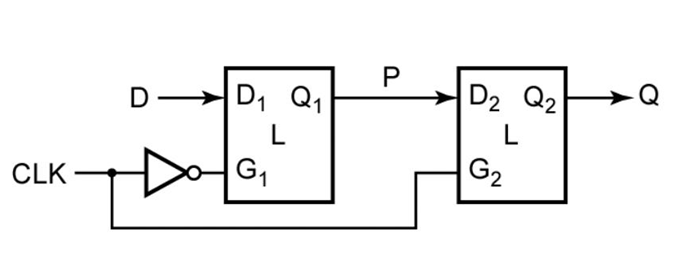

에지 트리거 회로가 구현되는 방법

에지 트리거 회로는 클록 신호가 변경되는 정확한 순간에만 응답하도록 단계별로 배열된 논리 게이트의 조합을 사용하여 구축됩니다.신호가 계속해서 통과하도록 허용하는 대신 회로는 클록 전환(에지)을 감지하고 잠시 동안 데이터를 캡처할 수 있도록 설계되었습니다.

이를 구현하는 일반적인 방법 중 하나는 마스터-슬레이브 구조라고도 불리는 2단계 설계를 사용하는 것입니다.이 설정에서 첫 번째 단계(마스터)는 입력 신호를 수신하고 두 번째 단계(슬레이브)는 값을 유지하고 출력합니다.이 두 단계는 클록 신호의 반대 위상에 의해 제어됩니다.클록이 한 상태에 있으면 마스터 단계가 활성화되어 입력을 캡처합니다.클록의 상태가 변경되면 슬레이브 단계가 활성화되고 출력이 업데이트됩니다.

이러한 배열의 결과로 출력은 클록이 안정적인 동안이 아니라 클록 신호가 전환되는 동안에만 변경됩니다.이는 내부 부품이 여전히 레벨 감지 요소를 사용할 수 있더라도 가장자리에 의해 트리거되는 동작을 효과적으로 생성합니다.

이 설계는 입력 데이터가 제어된 방식으로 전송되도록 보장하여 원치 않는 변경을 줄이고 회로의 신뢰성을 향상시킵니다.결과적으로 에지 트리거 구현은 플립플롭 및 기타 동기식 디지털 시스템에 이상적입니다.

에지 트리거 S-R 플립플롭

에지 트리거 S-R(Set-Reset) 플립플롭은 두 개의 제어 입력을 사용하여 저장된 값을 켜야 할지 꺼야 할지 결정하는 메모리 장치입니다.S 입력은 출력을 1로 설정하는 데 사용되고 R 입력은 출력을 0으로 지우는 데 사용됩니다.

이 플립플롭은 간단한 입력 규칙을 따릅니다.

• S = 1, R = 0 → 1을 저장

• S = 0, R = 1 → 0을 저장

• S = 0, R = 0 → 현재 값 유지

• S = 1, R = 1 → 허용되지 않음 (불안정한 출력이 발생할 수 있음)

S-R 플립플롭은 가장 초기이자 간단한 메모리 설계 중 하나입니다.주로 디지털 저장이 작동하는 방식과 제어 신호가 저장된 값을 변경할 수 있는 방식을 이해하는 데 사용됩니다.그러나 유효하지 않은 입력 조건으로 인해 고급 플립플롭 유형에 비해 현대 회로에서는 덜 사용됩니다.

에지 트리거 D 플립플롭

그림 7. 마스터-슬레이브 D 플립플롭 회로

에지 트리거 D(데이터) 플립플롭은 D라는 하나의 입력을 사용하여 단일 비트의 데이터를 캡처하고 유지하는 디지털 저장 요소입니다. D 입력을 내부적으로 안전한 제어 신호로 변환하여 S-R 설계에서 발견되는 모호성을 제거하므로 유효하지 않은 입력 조건이 없습니다.

클록이 전환되면 D에 있는 값이 출력 Q로 전송되어 저장됩니다.이렇게 저장된 값은 그 사이의 입력 변경에 관계없이 다음 클록 전환까지 안정적으로 유지됩니다.이러한 동작의 결과로 D 플립플롭은 제어된 데이터 샘플러처럼 작동하여 정확한 순간에 입력의 스냅샷을 찍습니다.

실제 회로에서 D 플립플롭에는 다음과 같은 추가 기능이 포함되는 경우가 많습니다.

• 설치 시간 – 입력은 클럭 에지 이전 짧은 시간 동안 안정적이어야 합니다.

• 대기시간 – 입력은 클럭 에지 이후 짧은 시간 동안 안정적으로 유지되어야 합니다.

• 전파 지연 – 클록 이벤트와 출력 변경 사이에 약간의 지연이 있습니다.

이러한 타이밍 요구 사항은 고속 시스템의 올바른 작동을 보장합니다.

에지 트리거 플립플롭의 장점 및 단점

에지 트리거 플립플롭의 장점:

정확한 타이밍 제어 - 특정 순간에만 출력이 업데이트되어 정확도가 향상됩니다.

안정적인 작동 – 입력 변동으로 인한 원치 않는 변화를 줄입니다.

향상된 동기화 – 공유 시계를 사용하여 시스템의 여러 부분이 함께 작동할 수 있습니다.

예측 가능한 동작 – 회로 설계를 더욱 쉽고 안정적으로 만듭니다.

글리치 감소 – 잡음이 많거나 불안정한 신호로 인한 오류 최소화

폭넓은 지원 - 최신 디지털 시스템 및 디자인 도구에 사용됩니다.

에지 트리거 플립플롭의 단점:

더욱 복잡한 설계 - 클록 관리 및 추가 회로 필요

클록 의존성 – 클록 신호 없이는 제대로 작동할 수 없습니다.

타이밍 제약 – 설정 시간, 유지 시간 및 지연을 신중하게 제어해야 합니다.

더 높은 전력 소비 - 클록 신호 및 스위칭으로 인해 전력 사용이 증가합니다.

전파 지연 – 클럭 에지 이후 출력이 즉시 변경되지 않습니다.

설계 민감도 - 잘못된 타이밍으로 인해 오류나 불안정한 동작이 발생할 수 있습니다.

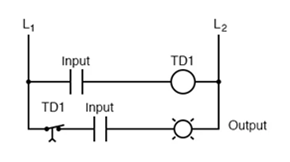

에지 트리거 플립플롭의 응용

그림 8. 릴레이 에지 감지 회로

레지스터 – 프로세서 및 디지털 시스템에 데이터를 저장하고 전송하는 데 사용됩니다.

시프트 레지스터 – 통신 및 데이터 처리를 위해 데이터를 단계별로 이동합니다.

카운터 – 타이머, 클록 및 디지털 측정 시스템의 클록 펄스 카운트

메모리 유닛 – RAM 및 기타 저장 회로에 데이터 비트 저장

데이터 동기화 – 공통 클록을 사용하여 시스템의 여러 부분 간 신호 정렬

디지털 시계 및 타이머 – 제어 타이밍 시퀀스 및 시간 기반 작업

상태 머신 – 순차 논리 회로에 상태를 저장하고 제어합니다.

주파수 분할 – 클럭 신호를 나누어 더 낮은 주파수 생성

파이프라인 시스템 – 고속 프로세서의 데이터 흐름 관리

결론

에지 트리거 래치 및 플립플롭은 정확하고 제어된 데이터 저장이 필요한 디지털 시스템의 필수 구성 요소입니다.특정 순간에만 출력을 업데이트함으로써 안정성을 향상시키고 오류를 줄이며 회로 동기화를 유지하는 데 도움이 됩니다.안정적이고 효율적인 전자 시스템을 설계하려면 이러한 장치의 작동 방식과 장점 및 응용 분야를 이해하는 것이 필요합니다.

뜨거운 기사

- LM358 듀얼 작동 증폭기 포괄적 인 가이드 : 핀아웃, 회로도, 등가, 유용한 예제

- CR2032 및 CR2016 상호 교환 가능합니까?

- 차이 이해 ESP32 및 ESP32-S3 기술 및 성능 분석

- 올바른 배터리 선택 : AG4, LR626, LR66, 177/376/377, SR626 및 SR626SW에 대한 가이드

- NPN vs. PNP : 차이점은 무엇입니까?

- ESP32 vs STM32 : 어떤 마이크로 컨트롤러가 더 낫습니까?

- BC547 트랜지스터 기본: 핀 배치, 응용 회로, 대체/보완 모델

- MOSFET이란 무엇이며 작동 방식은 무엇입니까?

- 전기 릴레이 기본 : 작업 작동, 유형 및 사용

- PNP 트랜지스터 : 구조, 작업 원리 및 응용 프로그램

SPDT 및 DPDT 시간 릴레이에 대한 간단한 안내서

SPDT 및 DPDT 시간 릴레이에 대한 간단한 안내서

2026-04-21

ATS와 STS: 차이점은 무엇입니까?

ATS와 STS: 차이점은 무엇입니까?

2026-04-21

자주 묻는 질문 [FAQ]

1. 디지털 시스템에서 래치보다 플립플롭을 선호하는 이유는 무엇입니까?

플립플롭은 클록 에지에서만 업데이트되므로 더 나은 타이밍 제어를 제공하여 시스템을 더욱 안정적이고 예측 가능하게 만듭니다.

2. 플립플롭에서 설정 시간을 위반하면 어떻게 되나요?

플립플롭이 불안정한 상태에 들어가 부정확하거나 예측할 수 없는 출력을 생성할 수 있습니다.

3. 플립플롭의 유지 시간은 무엇이며 왜 필요한가요?

홀드 시간은 올바른 데이터 저장을 보장하기 위해 클럭 에지 이후 입력이 안정적으로 유지되어야 하는 최소 시간입니다.

4. 플립플롭의 준안정성이란 무엇입니까?

준안정성은 입력과 클럭 신호 사이의 타이밍이 부적절하여 출력이 불안정해지는 조건입니다.

5. 클럭 신호 없이 플립플롭이 작동할 수 있나요?

아니요, 플립플롭에는 데이터 저장 시기를 제어하기 위해 클록 신호가 필요합니다.

6. 비동기식 입력과 동기식 입력의 차이점은 무엇입니까?

동기식 입력은 클럭에 의존하는 반면, 비동기식 입력은 클럭을 기다리지 않고 즉시 출력을 변경할 수 있습니다.

핫 부품 번호

08055A820JAT2A

08055A820JAT2A GRM155R60G106ME44D

GRM155R60G106ME44D CL31C333JBHNNNE

CL31C333JBHNNNE C1608C0G2A821K080AA

C1608C0G2A821K080AA C1005X7R1E152K

C1005X7R1E152K 0ZRM0010FF1E

0ZRM0010FF1E SI6415DQ-T1-E3

SI6415DQ-T1-E3 SMAZ5V1-13-F

SMAZ5V1-13-F IRLL024ZTRPBF

IRLL024ZTRPBF PIC32MX450F256L-I/PT

PIC32MX450F256L-I/PT

- MPC860DECVR50D4

- MAX931ESA+T

- MAX3097EESE

- MAX4208AUA+

- VI-27R-EW

- PS21964-4W

- MCIMX6Y1CVM05AB

- T491D226K020AT4513

- AM26S10CDR

- LT3513EUHF#PBF

- T495X477K010ATE045

- PBSS4360XF

- LM53603AQPWPRQ1

- TLC320AD545PT

- OPA1644AID

- TEA6856AHN/V205K

- T491D686K016ATAU047280

- STM32L432KBU6

- AT5665H_PBF

- BCM3383MRKFRBG

- CAT34FC02YI-TE13

- FSTU3253MX

- ISL6211CA

- M37704M4B-255FP

- MAX690AEPA

- PCF7953ATT/M1AC1500

- S9S12GA48MLF

- TMP82C265BF-2

- KIA7045AP

- S2L33M-A1-RH

- JS12-K

- R7F0C001G2DFB#AA0

- PFKC05-24S12

- MSM8660-1-AA

- K5N5633ATM-SF66T1V0

- CY7C1373D-133BZC

- 436500612

- RK73H1ETTP1152F

- FS300R12KE3/AGDR-71C